#### WMA -5

#### Heterogeneous Integration for WLP RF Transceivers : Challenges and Issues

#### Didier Floriot, Philippe Auxemery, Jean-Pierre Viaud

Semiconductors

United Monolithic Semiconductors

S International Microwave Sympos 2-7 June 2019 Boston, MA

- UMS motivation & strategy

- Heterogeneous Integration applied to RF Front End in mmWave

- SMART3 System in Package deployment

- Conclusion

- UMS motivation & strategy

- Heterogeneous Integration applied to RF Front End in mmWave

- SMART3 System in Package deployment

- Conclusion

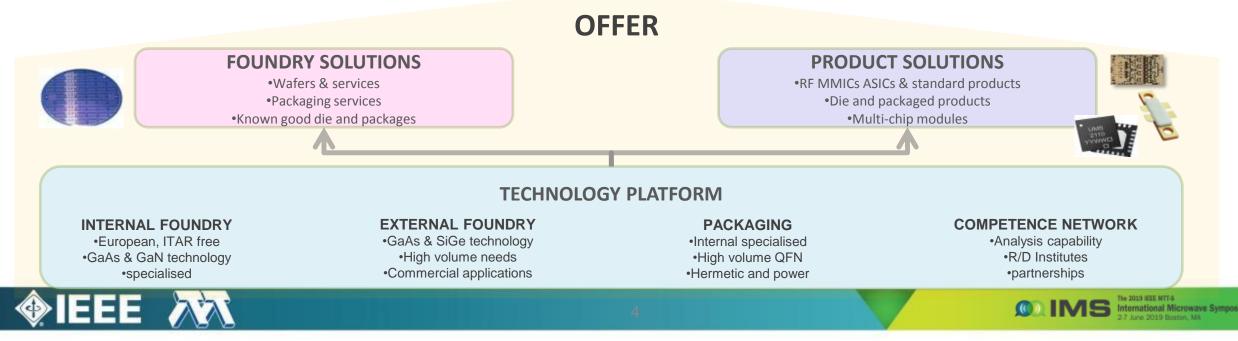

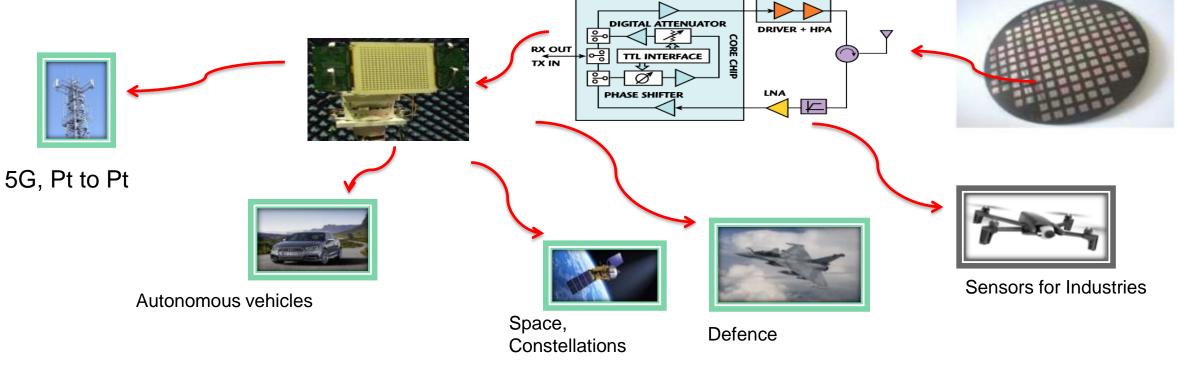

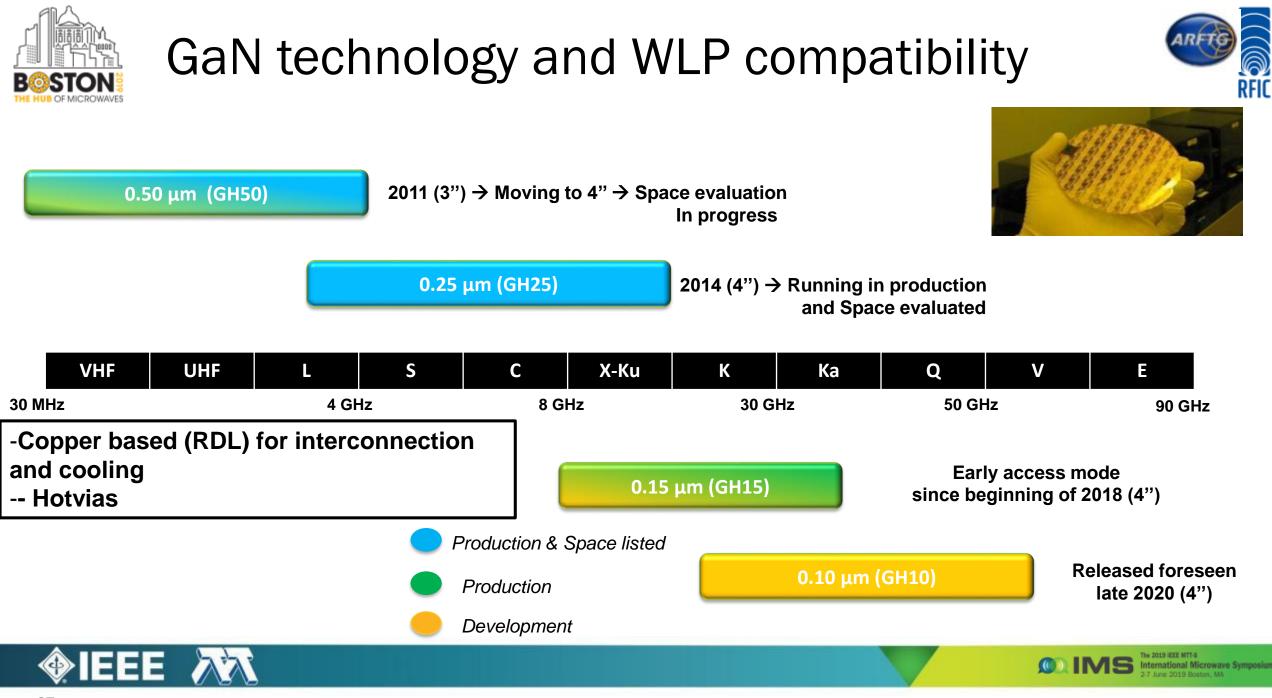

#### UMS offer, markets & technology platform

#### **DEFENCE & SECURITY**

•Phased array radar •Electronic warfare •Security applications

•Communication satellites •Earth observation •Scientific mission

#### **AUTOMOTIVE & SENSORS**

•24/79GHz short range radar •77GHz long range radar •Sensors/road tolling TELECOM

Point to point radio linksVSAT terminalsBase stations

- UMS motivation & strategy

- Heterogeneous Integration applied to RF Front End in mmWave

- SMART3 System in Package deployment

- Conclusion

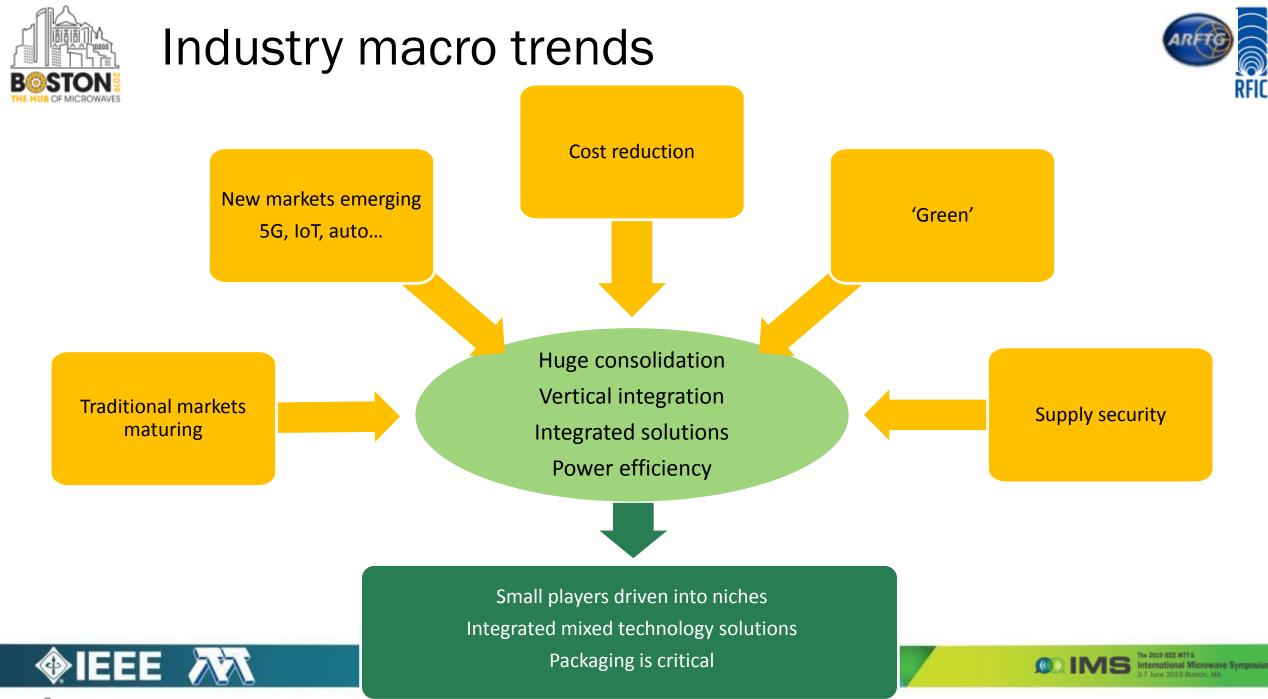

### Heterogenous integration applied to RF Front End up to Millimeter Wave ...

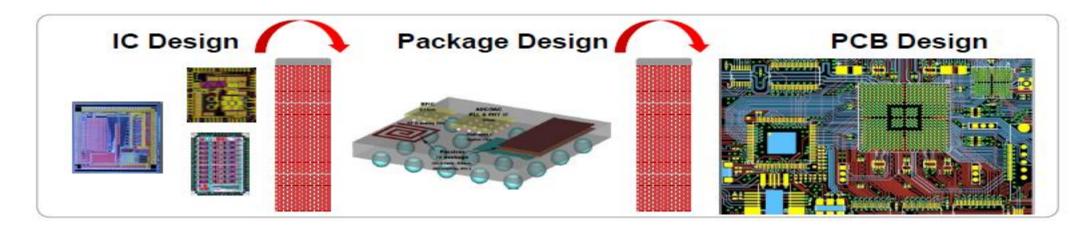

- What Is Heterogeneous Integration ?

- Related to the Integration of multiple bare die ICs, based on differing substrate materials and process technologies, into a single carrier (package/module).

- Size : from 0.1 to x mm

- Thickness : from 50 to 150 μm

- Technologies: GaAs, InP, GaN, CMOS, etc., and Process nodes: 32nm, 28nm, 16nm, 10nm,

- Side-by-side, stacked, flip-chip, wire-bonded, WLP, MEMS, IPDs, etc.

- Currently the most common method of integration is based on MCM/SiP technology

- Common platform for III-V device integration when Si cannot meet performance objectives

- Power

- Noise

- Losses

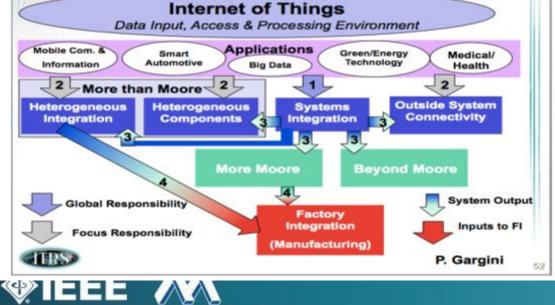

#### ITRS 2.0 – version 2014

RFIC

#### Wafer Level Packaging vs Panel Which domain for mmWave ?

Ithe 2019 IEEE MIT-5 International Microwave Symposium 2.7 June 2019 Boston, MA

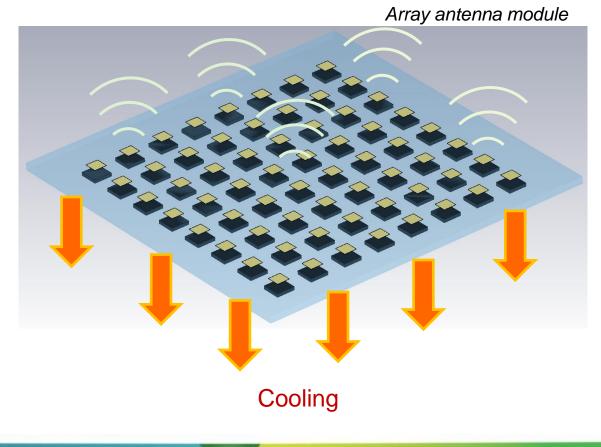

## Trigger : Active Antenna concept / MiMo

Need to integrate more and more complexity at Antenna level but footprint, weight and new applications are driving this demand

15 The 2019 IEEE MIT'S International Microwave Sympos 2-7 June 2019 Boston, MA

Trigger : Active Antenna concept / MiMo

Need to integrate more and more complexity at Antenna level but footprint, weight and new applications are driving this demand

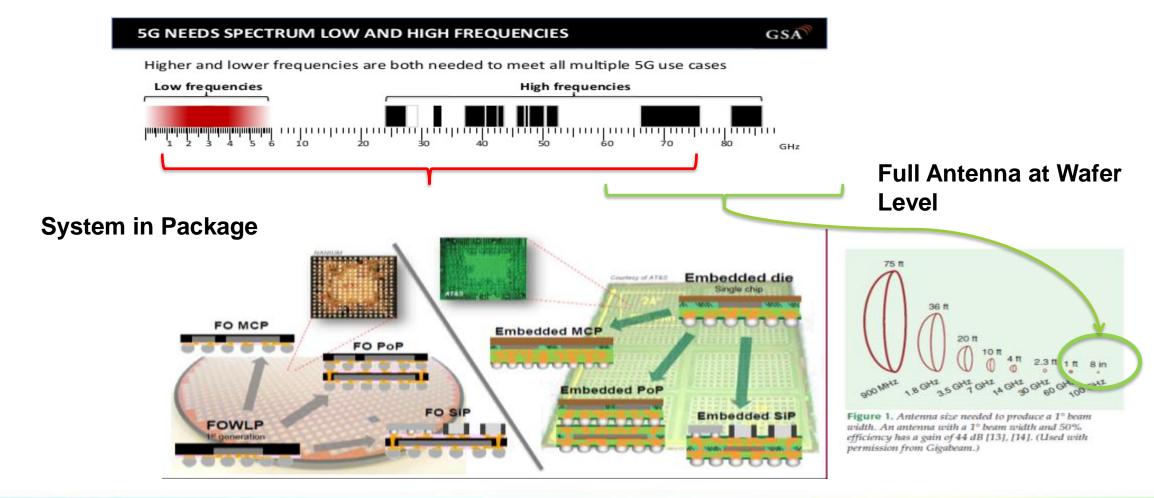

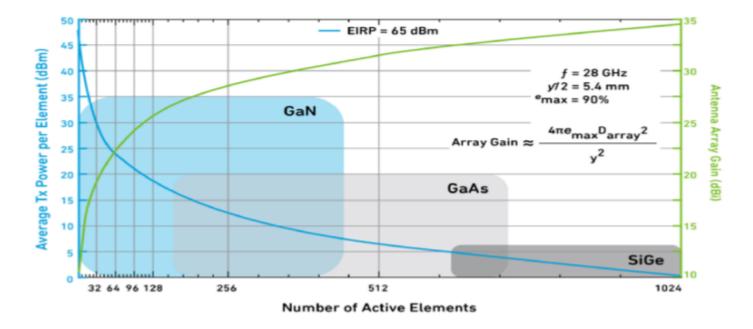

## 5G & Heterogeneous integration

- Trade off between the number of active elements

- PA power/channel reduces as number of elements increases for a given EIRP

- Beamforming circuitry becomes larger and more complex

- With enough elements is SiGe a good choice?

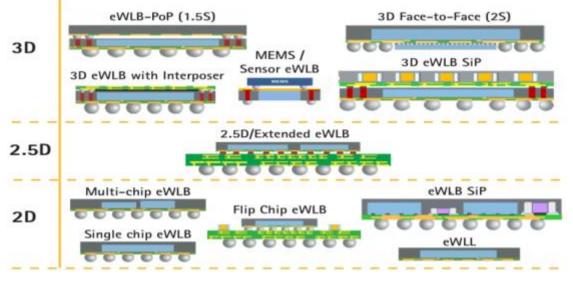

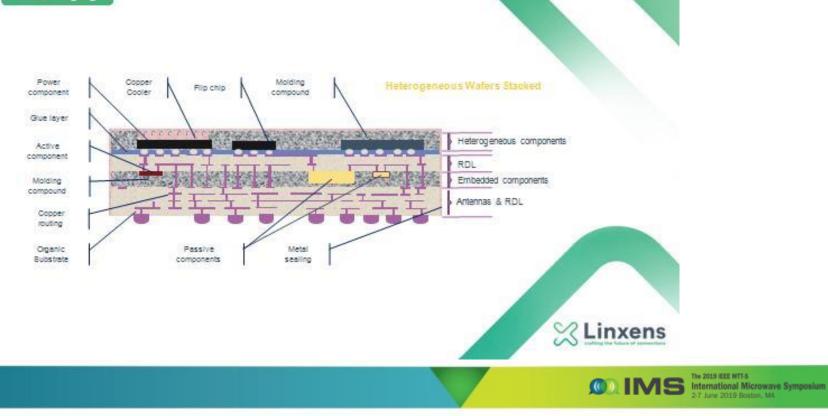

# Wafer Level Packaging Technologies – Fan-out based

- Many variants developed for WLP. What are the specific technical items specific to RF Front End, this platform should address ?

- Frequencies : from to C to E Bands ... (D ??)

- Dissipated Power : up to 30W CW → roughly 10 x 10 mm2 of footprint

- Max Surface : up to 15 x 15 x 0.5 mm2

- 3D compatible for Digital / RF integration → PoP or double RDL approach

- Improved cooling by one side

- Hermetically compatible

- Shielding & Isolation in between channels by appropriate metallic protection

- 125°C Back Side / MTF 20 years

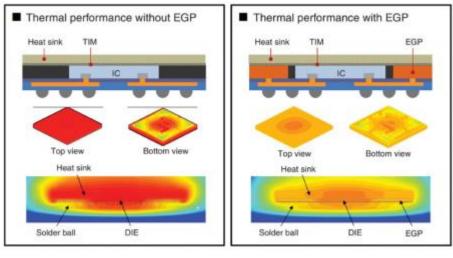

# Thermal management for active antenna systems

- Antenna transmission on one side of the PCB

- Thermal dissipation on the other side of the PCB

- → Less complex PCB design

- ➔ Cost efficient PCB

- ➔ Compatible with mesh size

| Type   | Theta Ja               | Theta Jb                | Theta Jc               | Remark                 |

|--------|------------------------|-------------------------|------------------------|------------------------|

| Type 1 | 46.0 K W <sup>-1</sup> | 18.37 K W <sup>-1</sup> | 7.13 K W <sup>-1</sup> | TIM material : polymer |

| Type 2 | 34.4 K W <sup>-1</sup> | 13.87 K W <sup>-1</sup> | 6.80 K W <sup>-1</sup> | TIM material : polymer |

International Microwave S

## WLP and parasitic reduction

| High                            | Package p               | parasitics    |              | Low          |

|---------------------------------|-------------------------|---------------|--------------|--------------|

| Resistance at DC                | 76 mΩ                   | 7.5 mΩ        | 3.2 mΩ       | ect          |

| Resistance<br>at 5 GHz/60 GHz   | 375 mΩ/ 1 Ω             | 41 mΩ/ 120 mΩ | 15 mΩ/ 45 mΩ | Interconnect |

| Inductance                      | 1.1 nH                  | 52 pH         | 18 pH        | Inte         |

| X                               |                         |               |              |              |

| A wire bond                     |                         | chip          | WLB          |              |

| A wire bond<br>Resistance at DC | BGA flip α<br>89 mΩ     | 22 mΩ         | WLB<br>32 mΩ |              |

|                                 | $\overline{\mathbf{v}}$ | 2             |              | Package      |

The 2019 IEEE MIT-S International Microwave Symposium 2-7 June 2019 Boston, MA

### Wafer Level Packaging Technologies – Fan-out based

- Many approaches and variant developed for WLP.

- Examples (among many ...)

(eWLB product portfolio Source: STATS ChipPAC)

(EDS technology from Infineon)

- UMS motivation & strategy

- Heterogeneous Integration applied to RF Front End in mmWave

- SMART3 System in Package deployment

- Conclusion

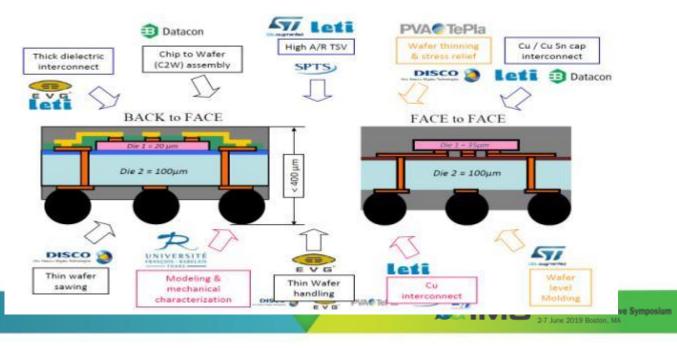

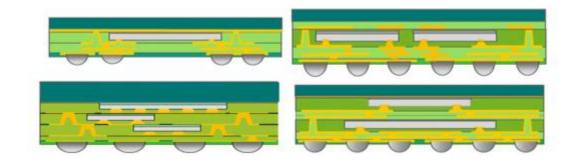

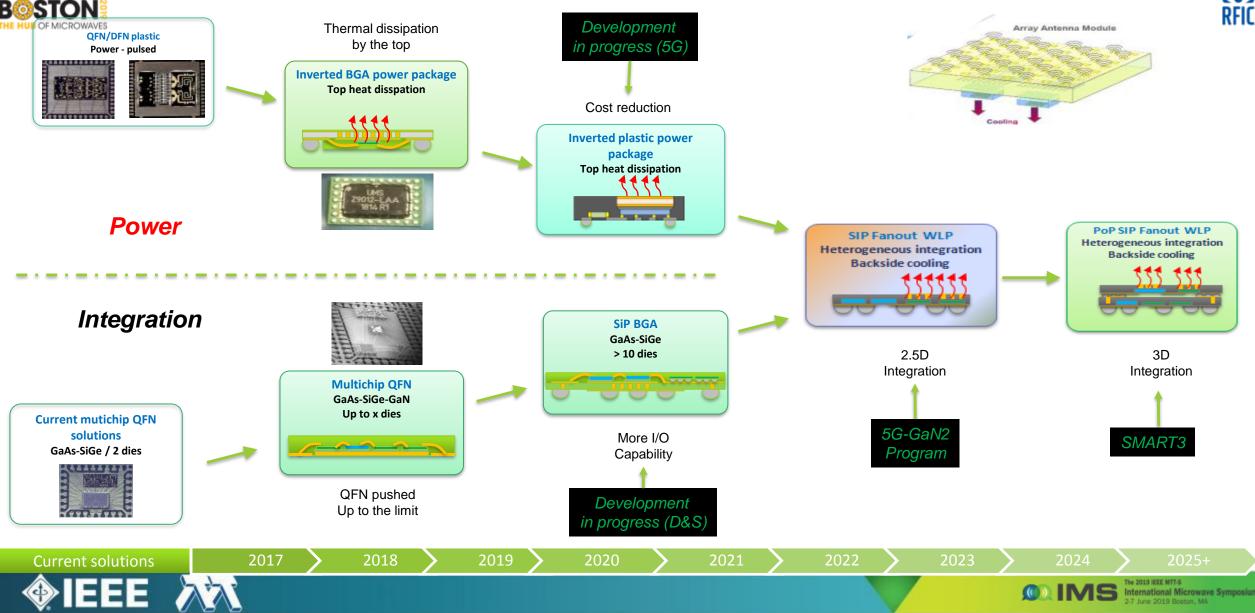

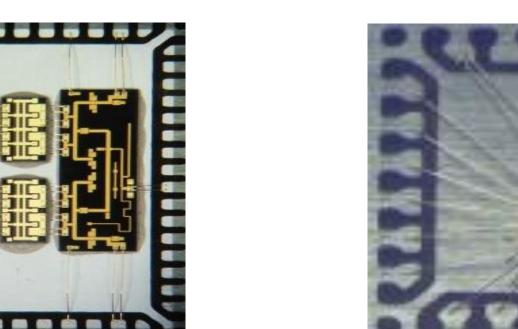

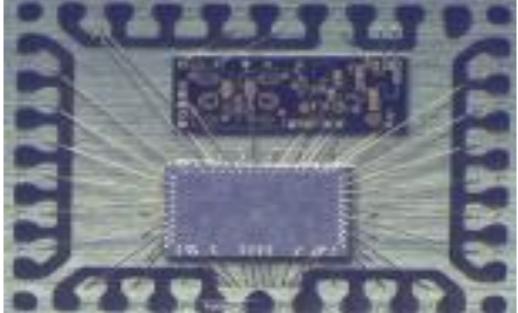

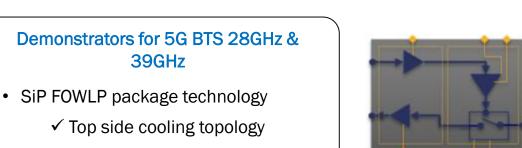

## SMART3 – SIP Technology development

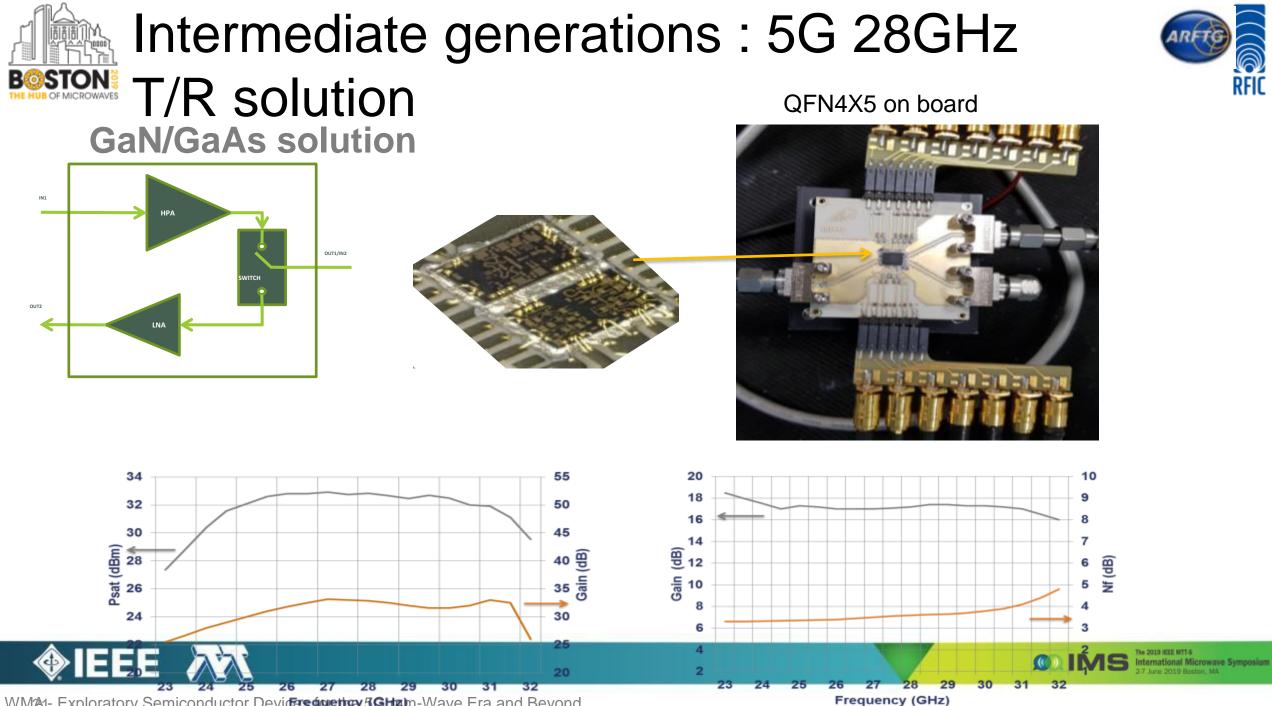

Intermediate generations : Examples of UMS mixed technology solutions

#### **Advanced telecom PA** GaAs & GaN – 28 GHz

#### Automotive transceiver GaAs & SiGe – 24 GHz

WM21- Exploratory Semiconductor Devices for the Semiconductor Devi

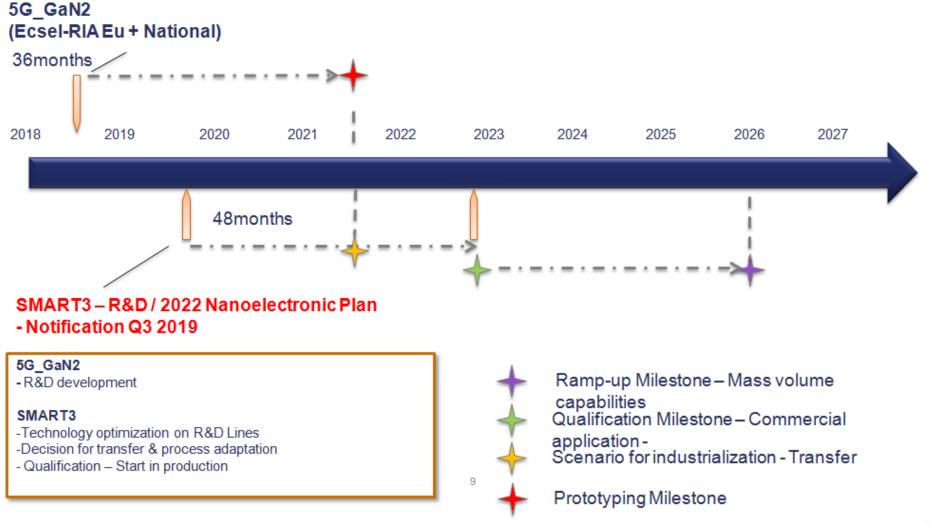

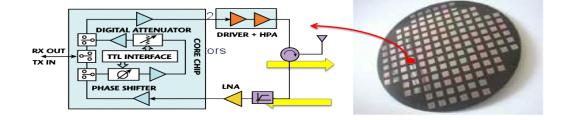

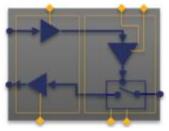

## Next steps for 5G & System In Package

Heterogeneous Integration: Wafer Level Packaging

• Compact RF Front End multi-technology demonstrators covering 28, 39 and 80 GHz based on innovative Wafer Level Packaging integration.

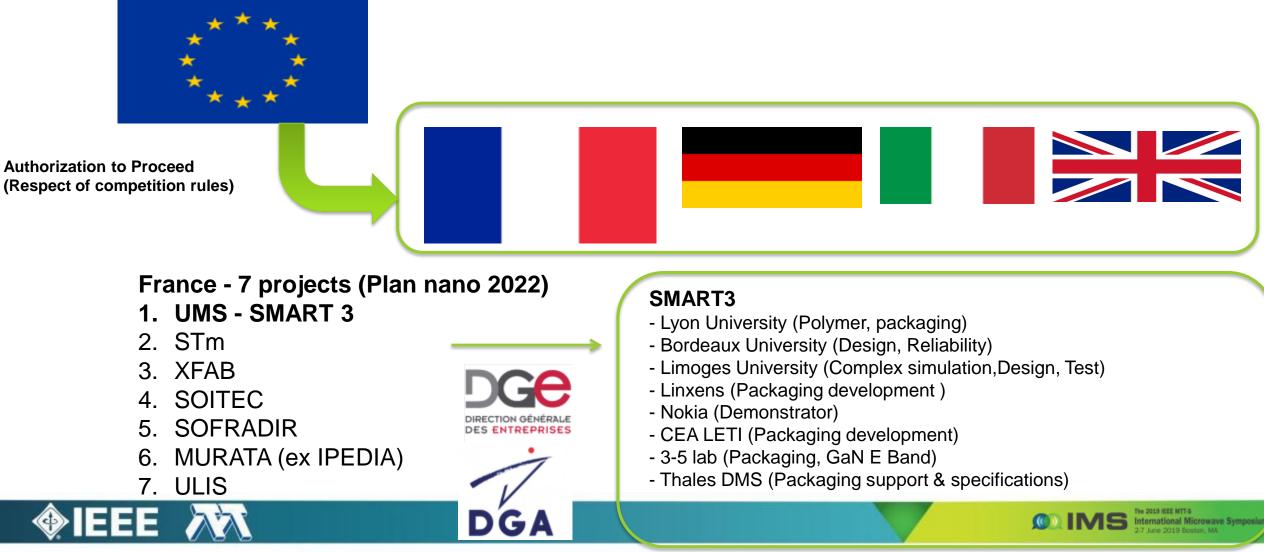

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 783274. The JU receives support from the European Union's Horizon 2020 research and innovation programme and France, Germany, Slovakia, Netherlands, Sweden, Italy, Luxembourg, Ireland.".

IMS

International Microwave Sy

2-7 June 2019 Boston, MA

#### <u>Three Domains</u>

- 3D advanced co-integration of Si / GaN power technologies System in Package (SIP)

- $\rightarrow$  TRL 5 to 6 in final

- <u>70% program effort</u>

- Millimeter wave GaN Technology for E-Band Radio

- $\rightarrow$  TRL3 to 4 in final

- <u>15% program effort</u>

- Ka-Band GaN compatible of 8" RFCMOS fab line for high density RF / mass market transceivers

- $\rightarrow$  TRL3 to 4 in final

- <u>15% program effort</u>

#### 5G\_GaN2 collaborative Project

- GaN & Packaging solutions for 5G

- https://www.5ggan2.eu/ ۲

- 17 European partners ullet

- UMS as project coordinator •

- 3 years project 2018-2021

✓ Integration / Miniaturization

|                                                                 | III-V lab                | Benetel                                   | Ceatech                                        | ERICSSON                                         |

|-----------------------------------------------------------------|--------------------------|-------------------------------------------|------------------------------------------------|--------------------------------------------------|

| Coordinator<br>United Monolithic<br>Semiconductor SAS           | 3-5 Lab                  | Benetel                                   | CEA Leti                                       | Ericsson                                         |

| Fraunhofer                                                      | MC                       | mpg.                                      |                                                | :::: S T U                                       |

| Fraunhofer Institute of<br>Applied Solid-state<br>Physics (IAF) | MEC                      | Molecular plasma group<br>former Funcoats | Sencio                                         | Slovak University of<br>Technology in Bratislava |

| SweGaN                                                          | <b>TESAT</b>             | THALES                                    |                                                | <b>6</b>                                         |

| Swegan                                                          | Tesat Spacecom           | Thales CS                                 | United Monolithic<br>Semiconductor GmbH<br>UMS | University College Dublin                        |

|                                                                 | Concession in the second |                                           | <b>≫FAB</b>                                    |                                                  |

|                                                                 | University of Padova     |                                           | X Fab Semiconductor                            |                                                  |

WMA - Exploratory Semiconductor Devices for the 5G mm-Wave Era and Beyond

International Microwave Sympo

### IPCEI : Important Project of Common European Interest

- WLP Technology development and assessment

- Polymer formulation and adaptation

- Compatible of High T° / CTE /

- Modelling

- EM 3D, Thermo-mechanical, Electrical → PDK

- Reliability

- Evaluation, Pre-qualification

- Demonstrators

- 5G in Ka Band, V-Band, E-Band

13

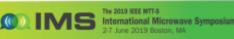

WLP technology applied to power and mixed Analog / Digital RF FE

- Test Vehicle by Building block of the WLP process

- Evaluate Mechanism of End of Life

- Associated to Energy of Activation

- Evaluate Maximum Ratings

| Stress test                                  | Standard/spec                                                                           | Pass criteria  |

|----------------------------------------------|-----------------------------------------------------------------------------------------|----------------|

| Moisture sensitivity level (MSL)             | EIA/J-STD-020C<br>(Level 1)                                                             | MSL 1          |

| High temperature storage (HTS)               | JESD22-A103<br>(Ta: 150 °C)                                                             | 1000 h         |

| Temperature cycling (TC)                     | JESD22-A104<br>(Cond B: 55–125<br>°C)<br>Preconditioned<br>(Level 1; Tr: 260<br>°C)     | 1000×<br>1500× |

| Unbiased HAST (uHAST)                        | JESD22-A118<br>(Cond A: 130<br>°C/85% RH)<br>Preconditioned<br>(Level 1; Tr: 260<br>°C) | 96 h<br>188 h  |

| Temperature humidity bias<br>(THB)           | JESD22-A101<br>(85 °C/85% RH,<br>VCC)                                                   | 1000 h         |

| Temperature cycling on board<br>(TCoB JEDEC) | IPC 97-01<br>(-40 °C/+125 °C, 1<br>cy h <sup>-1</sup> )                                 | 500×<br>1000×  |

| Temperature cycling on board                 | NOKIA spec.                                                                             | FF > 500 cycle |

## SMART3 - Modelling strategy

• Standard approach – step by step but inappropriate

- Subscription Complete toolbox for co-design a complex SIP

- → Develop a complex model approach

- UMS motivation & strategy

- Heterogeneous Integration applied to RF Front End in mmWave

- SMART3 System in Package deployment

- Conclusion

### Conclusions

- WLP as an extension of FE process / foundry offers

- Opportunity to design and produce a new generation of RF products

- Integration / Performances / Cost / Supply chain

- SMART3 presents an alternative for low to medium volumes

- Communication (5G, Backhauiling, ..

- Strategic domains (Aerospace, Security ..)