### 5G GaN2

Heterogeneous integration of state of the art Semiconductor Technology

#### **Strategic Objective**

5G\_GaN2 has as major objective to develop new industrial disruptive technologies from semiconductor to integration. It will support the birth of new sub system architectures and target the steps in performances for the 5G generation from Ku to E bands for BTS, point to point & SATCOM communication networks

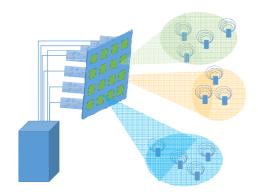

Phased antenna arrays are a vital part of the newly emerging 5G technologies. Thanks to the ability of beam-forming and beam-steering spatial diversity is achieved. The spatial diversification is reached by enabling control over the shape and direction of the antenna's radiation pattern.

The radiating elements of phased antenna arrays ought to be spaced by about 0.5λ. At 30GHz, the mesh of the antenna is about 5mm, therefore transmit and receive RF components must be smaller then 5X5mm<sup>2</sup>

#### www.5ggan2.eu

Start date:

Duration:

Total costs:

Number of participants:

Number of countries:

Project coordinator:

1 June 2018

36 months

21 M€

17

Number of participants:

9

Project coordinator:

Philippe Auxemery

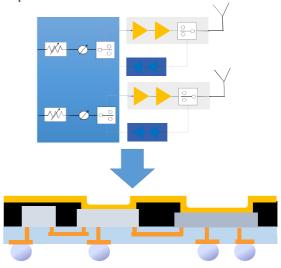

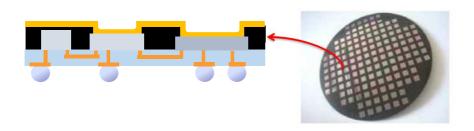

### Fan Out Wafer Level Packaging benefit

- High integration

Active and passive dies

Short interconnections

- Heterogeneous integration

Mix of state of the art technologies for RF and digital functions

- Top side thermal contact

### **Advanced Semiconductor Power Technologies**

•0.15 μm GaN on Si technology compatible of 8" inches CMOS line

•mmWave 0.08μm GaN on SiC power technology

## 5G GaN2

Heterogeneous integration of state of the art Semiconductor Technology

5G RF Front End 24-30GHz mixed GaN/GaAs

39GHz RFSOI Switch

#### 80GHz 2W GaN High Power Amplifier

Compact RF Front End demonstrators covering 28, 39 and 80 GHz based on innovative Wafer Level Packaging integration

- 3D integration

- New system architecture

- Mixed of RF and digital functions

# YOUR PROJECT NAME

ECSEL JU SYMPOSIUM June 17-18 2019

# YOUR PROJECT NAME

ECSEL JU SYMPOSIUM June 17-18 2019